实际案例解析PCB传输线损耗设计

ChatGPT的横空出世预示着AI时代已经到来,AI时代将是比拼算力的时代。高算力在PCB上的表现就是超高信号传输速率,这预示着AI时代将极大推动高速PCB在质和量上的需求,同时将大幅增加高速PCB信号完整性SI设计与制造加工上的难度。以当前的高速传输总线SI的要求来看,PCB的传输线设计与控制早已经不是像当年那样最多控制个阻抗,线宽和叠层几乎是想怎么设计就怎么设计时代了。现在板子一大,线长轻松10inch以上,可能还会有过孔和连接器。这时,PCB传输线的损耗就是我们设计中不得不考虑的问题,而且是越来越具有挑战性的课题。

那影响损耗的因素有哪些呢?实际上损耗影响因素非常多,相邻线的串扰,阻抗不匹配,辐射和PCB上影响阻抗的因素都会对损耗造成影响,但最关键最主要的损耗来源还是PCB传输线本身,我们知道PCB传输线不是理想的而是有损传输线。一般的传输线损耗有两个主要的部分,一个是介质损耗(主要是基材的DK/DF性能影响),另一个是导体损耗(粗糙表面的趋肤效应影响)。

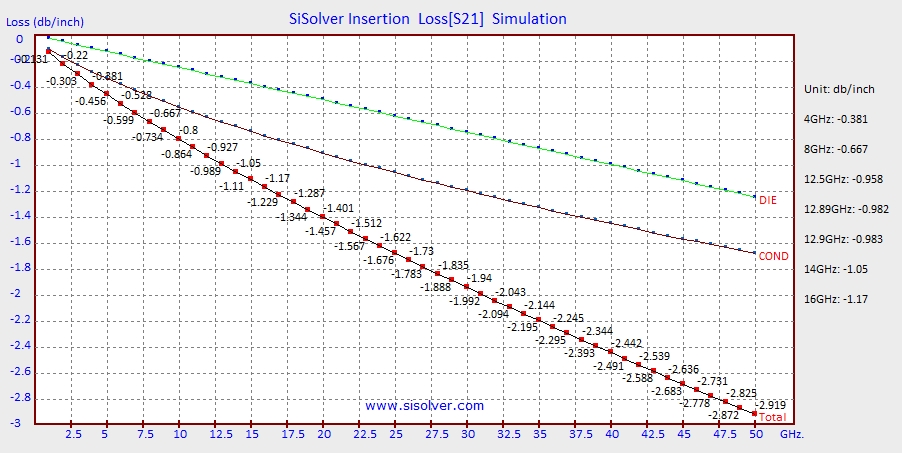

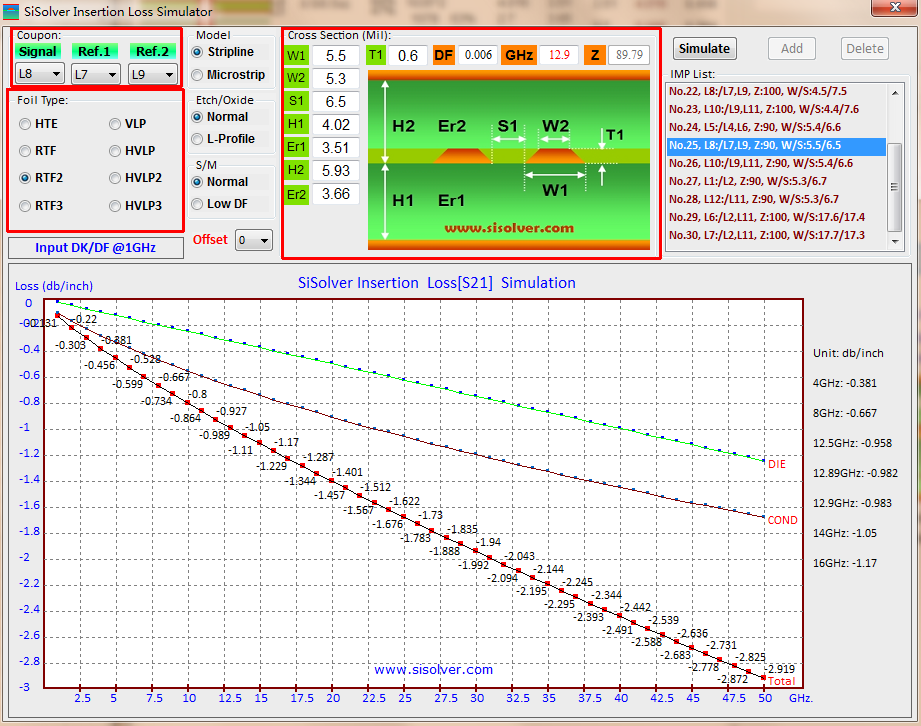

有哪些参数是我们可以在设计中控制的呢?甚至更深入一步,用什么基材和叠层可以满足到损耗要求呢?下面我们通过实际案例来具体说说怎么通过设计来控制损耗。下图是SiSolver的传输线模型仿真参数和结果显示界面,我们选择最常见的内层差分线做演示。图中“Cross Section”区域可以设定线宽,间距,铜厚,以及到参考层的介质厚度等参数;“Foil Type”区域选择铜箔类型(决定铜箔粗糙度),编辑选择完成后,点击Simulate即可得到如图中所示3条损耗仿真线,单位是db/inch。其中DIE表示介质损耗,COND表示导体损耗,Total表示介质和导体的总损耗。

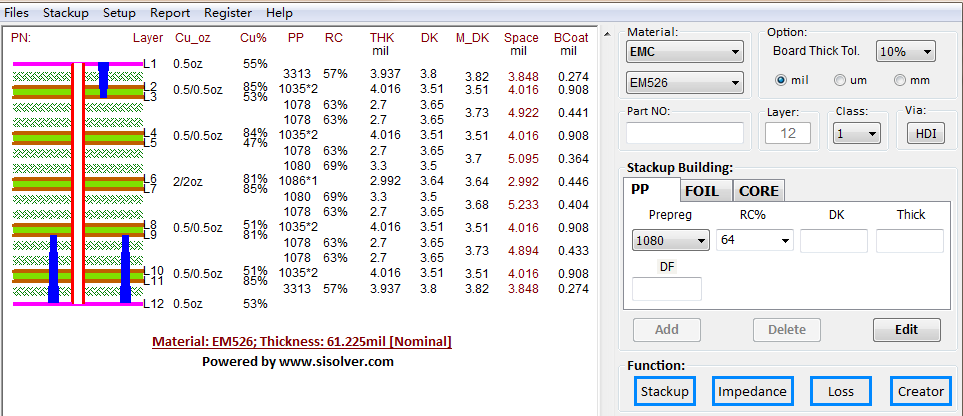

如果想要精确的评估实际叠层中某层上传输线的损耗,那么可以在软件中选择基材并建立叠层如下图,然后在上图中“Coupon”区域选择信号层和参考层,软件自动获取叠层介厚和DK参数填入到“Cross Section”区域中。这样你不仅可以调整线宽间距,还可以自己选择基材和叠层结构来快速评估并确定最优的设计方案。

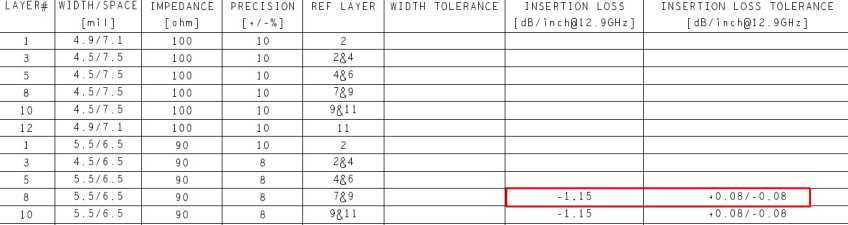

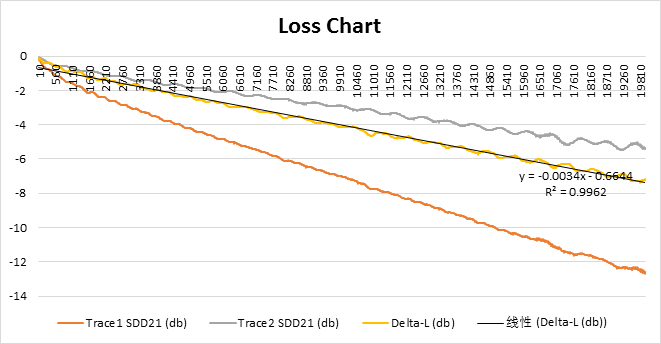

最后给出案例的损耗设计规格和实际投板加工后的损耗实测结果:客户12.9GHz插损规格是-1.1db/inch;仿真值-0.983db/inch,实际投板后实测SDD21均值-1.01db/inch。SiSolver在PCB加工制造端有近10年的叠层阻抗损耗一体化仿真研发和量产数据验证的积累,其仿真精度可以替代部分打样测试,快速准确评估实际叠层的SI性能与方案设计。